1. 介绍

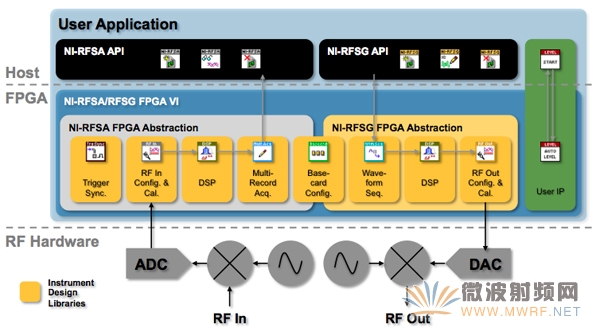

NI VST FPGA软件包含多层代码,提供了从底层控制到高层抽取的一切,拥有RF信号分析仪和RF信号发生器的功能。底层组件实现了具体硬件的标准功能,包括信号校准、前端控制,以及基于记录的采集和生成,被称为仪器设计库。这些库提供了互相匹配的主机和FPGA代码对,并且可以聚集以构建完整的硬件设计。LabVIEW项目样例包含了基于仪器设计库的相关主机和FPGA代码,提供了开发各种应用所需要的模板。另外,NI-RFSA和NI-RFSG仪器驱动还支持VST仪器驱动FPGA扩展,使VST FPGA源代码完美适合具体应用。

2. 仪器设计库

NI提供矢量信号收发器所用的多种仪器设计库。如上文所述,这些仪器设计库存在于用户和生产厂商的关于主机端和FPGA的代码中,,实现了仪器的常见功能。表2列出了一些顶层仪器设计库及其功能。

表1. NI VST所用顶层仪器设计库。

ni.com/vst/getting-started/zhs/所列软件安装了这些仪器设计库,在硬盘的c:\Program Files\National Instruments\LabVIEW [version]\instr.lb\位置。这些库具有颜色和谐的粗边框,与其他VI明显有别。

图1:仪器设计库具有颜色和谐的粗边框,此独特图标使其与其他VI相区别

另外,这些库在默认情况下处于锁定状态,用户在修改内容之前,需要先通过会话框将VI解锁。下文所述是使用这些仪器设计库的详细信息,适用于任何更改。

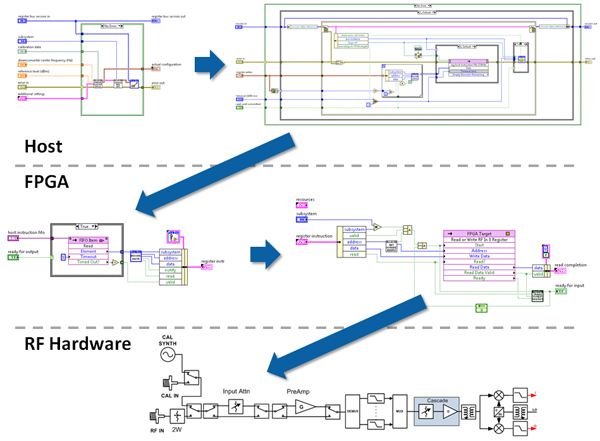

在给定仪器设计库的主机与FPGA之间交换数据可采用多种机制。所有采用LabVIEW RIO架构和LabVIEW FPGA的NI产品均使用NI-RIO驱动,此驱动提供了单点方式的、存储器映射、基于寄存器的主机至FPGA以及FPGA至主机通信,还有从主机至FPGA以及FPGA至主机的多点连续DMA FIFO。这些都是功能强大的数据交换机制,实现主机与FPGA之间的有效通信不需要了解或者只要些许了解底层总线架构。

仪器设计库的一个常见要求是:主机代码需要将大量的设置下载到设备中,例如要对与FPGA相连接的芯片寄存器进行编程,或者更新设置组,例如FPGA上的滤波器抽头。由于一些仪器设计库要求采用此策略,并且设备的DMA通道数目有限,所以这些库可能需要共享一个FIFO,从而需要在主机端和FPGA端增加额外的逻辑来实现。另外,对于大数据集来说,此类通信一般为单向,但是可能也需要提供从FPGA至主机的某种单点确认,例如确认所有设置均已成功应用等等。所有这些概念组成为一个单独概念,称为寄存器总线,并为一些仪器设计库所采用。

寄存器总线使用一个主机到FPGA端的DMA FIFO来下载设置,以及一些寄存器/NI-RIO控制器和指示器,用于握手,将单点数据返回主机,或者发出信号,确认已下载设置中的指令已经应用。

图2. 寄存器总线是基于NI-RIO DMA、控制器和指示器构建的轻质协议,实现了大量设置组至FPGA的高效下载,这是给定仪器设计库的主机与FPGA侧之间的常见要求。

[page]为了完成仲裁,每个仪器设计库均有一个独一无二的子系统ID,从而使得多个库能够共享一条寄存器总线。为了更好地总结VST仪器设计库的通信策略,表2说明了每个库所采用的策略。

| 控制器和指示器 | DMA FIFOs | 寄存器总线 | |

| DSP | X | – | – |

| RF In | – | – | X |

| RF Out | – | – | X |

| Basecard | – | – | X |

| 多记录采集 | – | X | X |

| 波形序列器 | – | X | X |

| 触发同步 | X | – | – |

| 嵌入式配置 | – | – | X |

表2. NI PXIe-5644R仪器设计库的主机与FPGA数据交换机制。

另外,通过与嵌入式配置仪器设计库配合使用,寄存器总线还可以在不牵涉主机的情况下完成FPGA触发的重新配置。

由于仪器设计库代表了卖主与用户代码之间的已定义接口,所以位于主机和FPGA两者的调色板上。在LabVIEW VI方块图的主机情境下,仪器设计库的主机侧接口见于Functions>>FPGA Interface>>NI PXIe-5644R 或者 Functions>>FPGA Interface>>NI PXIe-5645R。在FPGA侧,则位于Functions>>NI PXIe-5644R 或者 Functions>>NI PXIe-5645R下。

VST仪器设计库的主机调色板

VST仪器设计库的FPGA调色板

图3. NI VST仪器设计库的主机和FPGA调色板。FPGA调色板包含了实现常用底层功能的其他仪器设计库

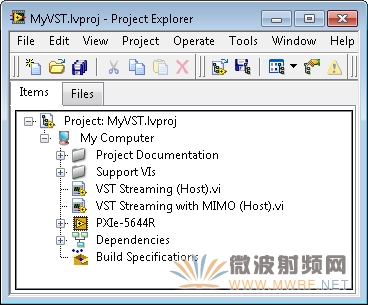

3. LabVIEW项目样例

NI VST仪器设计库的能力强大,但是并不能单枪匹马地完全满足软件设计仪器实现默认功能的要求,也不能提供大多数VSA和VSG仪器编程人员所熟悉的简单主机接口。

LabVIEW 2012提供了一个新功能,这种方便的机制不仅能够分配附加代码,从而提供默认、预编译的功能和一个方便的主机接口,而且还使用户能够轻松地掌握这些代码。此机制是LabVIEW项目样例,将LabVIEW项目、具体VI,以及相关文件复制到用户指定的硬盘位置。另外还提供文件重命名和更新VI标题的能力。

图4.利用LabVIEW 2012项目样例,软件设计仪器的用户可以完全掌握代码的相关部分。

欲了解创建NI VST项目样例的详细信息,请访问ni.com/vst/getting-started/zhs/。

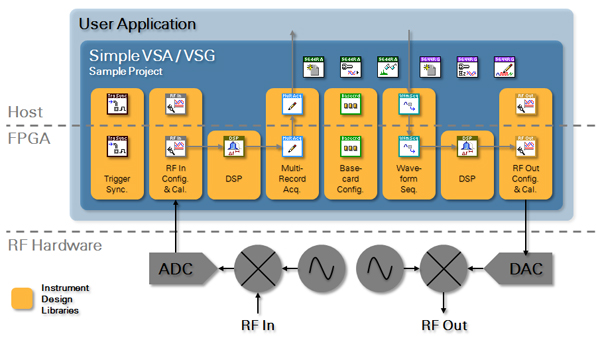

NI PXIe-5644R的软件安装程序能够创建具有不同特征的多个项目样例。最类似于默认VSA和VSG功能的项目是Simple VSA/VSG项目样例。此项目样例提供了与其他VSA和VSG API相似的主机接口。Simple VSA/VSG项目样例的高层架构和数据流如图5所示。

[page]

图5. Simple VSA/VSG项目样例在主机和FPGA上聚集仪器设计库,提供了一个VSA和VSG用户所熟悉的起点

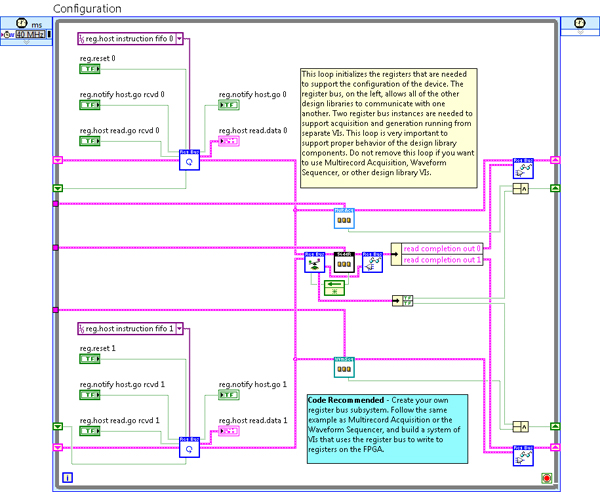

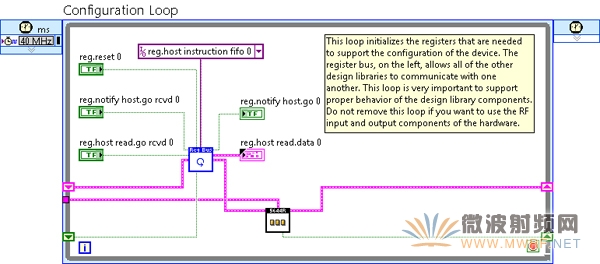

从Simple VSA/VSG项目样例的FPGA VI开始,有四个主要回路,一些附加功能位于过程subVI内。为配置NI VST的所有可编程组件,以及FPGA上的一些仪器设计库,配置回路从主机处接收寄存器和设置,然后将其分布至各个FPGA子系统和外部电路。为了提高性能以及使主机上的多个过程均能够独立访问,有两个寄存器总线。一个用于采集,另一个用于生成,并且每一个都必须能够配置共享资源,例如计时。

图6. 配置回路负责接收主机的数据以及对仪器进行编程

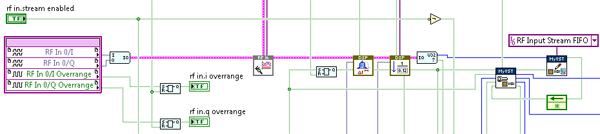

RF输入回路获取模数转换器(ADC)的数据;进行复矢量校准;并进行频移、相位校准、减损,以及可变、部分、防混叠抽选。另外,RF输入回路还实现了同步以及数字式功率水平触发,然后将数据写入FIFO,并最终写入DRAM。

图7. RF输入回路以可配置I/Q速率生成已校准数据,并将其写入DRAM。

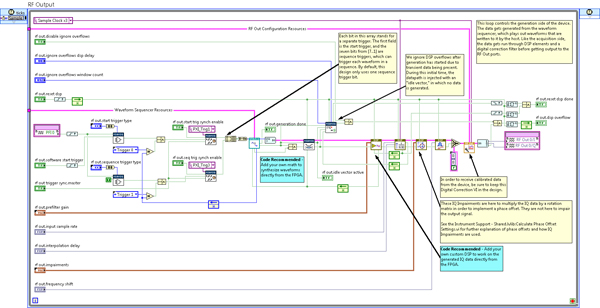

RF输出循环类似于RF输入循环,但是操作顺序相反。来自DRAM的数据进行内插、定标、频移、相位校准、内插、校准,然后通过数模转换器(DAC)生成。另外还有触发和同步所用信号。

图8. RF输出循环检索来自DRAM的数据然后生成数据

过程子VI包含有循环和状态机,实现了多数据记录采集和DRAM控制器对波形的排序。这些子VI包含了大量代码,满足了大带宽和低滞后性能要求,确保这些子VI能够在全速率ADC数据转换下溢出,以及产生全速率DAC数据而不发生下溢,同时仍然与主机之间进行波形数据传输。

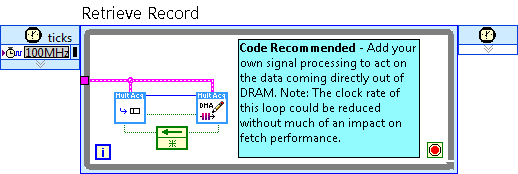

读取循环实现的功能可以存在于多记录采集过程之内,然而为了方便起见而将其显示出来。该循环可以再数据离开DRAM时并在被发送到主机前进行数据处理。此路径在它自己的回路之内,从而那些并不符合120 MHz RF输入和输出回路的定时要求的IP仍然可以使用。为了适应这种IP,稍微降低此回路速率并不会影响读取性能,然而如果降得过多,则只会增加数据到达主机所需时间。这样即使采样内存被填满了,也不会丢失样点或破坏数据。

[page]

图9.读取循环提供了在已采集数据返回主机之前对其进行处理的机会。在默认情况下,读取回路返回原始数据。

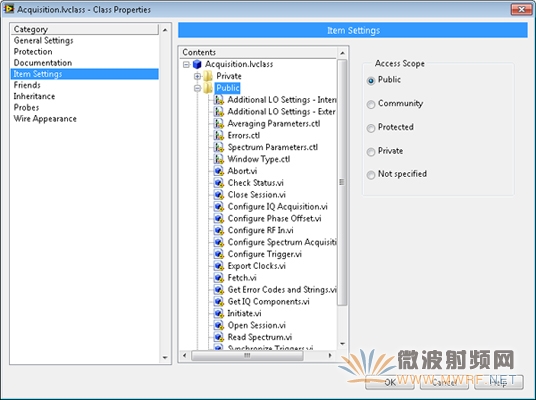

虽然顶层FPGA VI集合了13个仪器设计库的功能,然而在主机上对所有这些库进行独立编程仍然不方便,并且此应用层主机代码一点也不像传统的VSA或者VSG API。为了解决此问题,Simple VSA/VSG项目样例包含了一个附加主机层,将这些仪器设计库集合在一个接口内,提供了与供应商定义的VSA/VSG API相类似的功能。LabVIEW类为此提供了一个方便的机制,即提供一个严格类型的会话,公有和私有方法,以及一个方便的子VI图标头文件保持机制。请注意,LabVIEW类中面向对象的继承,并没有用于此主机接口。

图10.LabVIEW类提供了一个方便的功能集合和主机接口保持机制。

这个简单的VSA/VSG样例项目还提供了常见的RF VSA和VSG操作所用的若干个主机样例,这些样例说明了如何正确使用主机接口。这些样例涵盖频域和I/Q采集;CW和基于序列的波形发生;以及多输入多输出(MIMO)同步。

图11.一些主机样例说明了Simple VSA/VSG项目样例使用基于类的主机接口的方法

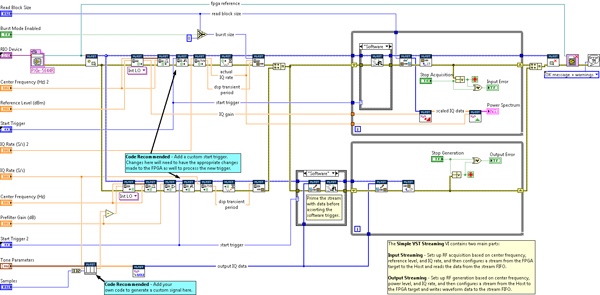

简单VSA/VSG项目样例包含极多功能,并提供了熟悉的主机接口。然而该实用工具的代价就是代码的复杂度。具体地说,FPGA上的DRAM采用基于波形的抽取,显著增加代码量、复杂度,以及VST FPGA资源占用。然而,并不是所有应用均需要基于波形或者仪器数据移动范式。一些应用更加适合实时流数据移动架构。对于这些应用,VST Streaming项目范例是一个更好的起点,自定义的自由度更广。

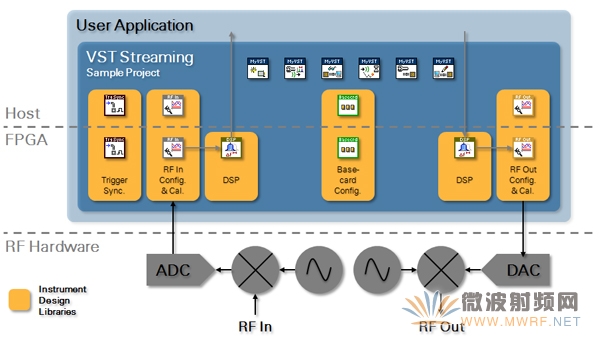

图12.VST Streaming项目样例在主机和FPGA上集合了仪器设计库,提供了一个灵活地开发实时、低滞后信号处理和嵌入式应用的起

VST Streaming项目样例的顶层FPGA VI的架构与简单VSA/VSG项目样例相近。然而如果仔细考察,会发现要简单得多。可以明显看出,VST Streaming没有代码量极多的配置过程。配置循环也简单得多,只有一条寄存器总线而非两条,并且所有子系统均包在一个子VI中。

图13.VST Streaming项目样例中的FPGA VI配置回路,只有一个寄存器总线接口,比Simple VSA / VSG要简单得多

[page]VST Streaming项目样例没有独立的采集和发生循环,而是所有模拟I/O均采用一个循环。对于要求RF输入输出之间的相位关系已知的应用,由于ADC和DAC使用相同的采样时钟,此架构提供了两者之间的确定性同步。DSP和VST Streaming项目样例的校准类似于VSA / VSG。

两个项目样例FPGA VI之间的主要区别是:VST Streaming项目样例使用轻质机制完成与主机之间的数据收发。它采用简单的流控制器,支持基本触发、连续和间断流,以及溢出和下溢检测。这些控制器中断信号源与目的地之间的2线握手信号,有效地选通数据流。控制器不支持全4线握手方案,该方案能够调整上游节点或者被下游节点所调整;因此,系统特性化以及确保这些流控制器控制的所有FIFO均能够以要求的速率产生或消耗数据就落到了程序员的肩上。在VST Streaming项目样例中通过简单的更改默认情况下完成与主机之间的数据收发的FIFO,可以支持数据流传输到VST FPGA上的其他位置以进行进一步处理,或者通过PXI Express背板,利用P2P传输至其他模块。

图14.FPGA流控制器和FIFO封装实现基本流控制,并且能够轻松改变数据流的源及目的地路线。

现在来看VST Streaming项目样例的主机端,虽然机制与Simple VSA/VSG不同,也存在类似于仪器设计库主机组件的集成,。VST Streaming项目样例不使用LabVIEW类,而是将功能简单地集成到子VI中,并将会话传递至子VI之间的寄存器总线。此寄存器总线会话还包含有FPGA VI 引用,因此所有这些子VI不仅能够访问寄存器总线通信策略,而且还可以访问NI-RIO FIFO和控制器。另外,不存在独立的数据采集和生成会话;所有VI均使用同一会话。

图15.VST Streaming项目样例主机接口具有一个基于寄存器总线的会话线,用于采集和生成subVI。在逻辑上,此样例将采集和生成分组成为独立的行,以方便阅读。

VST Streaming项目样例提供两个主机样例。较简单的一个样例把从VST处采集得到的增多的或者连续的波形数据传输至VST进行生成,。比较高级的样例说明了多个VST的MIMO同步。

图16.这些样例说明了VST Streaming项目样例的主机接口

4. 仪器驱动FPGA扩展

仪器驱动FPGA扩展提供了一种兼容NI-RFSA和NI-RFSG仪器驱动的VST FPGA编程方法。FPGA上的抽取层实现了所需要的仪器驱动功能,同时提供接口以改善具体应用的FPGA。虽然不像仪器设计库的直接编程那样灵活,然而仪器驱动FPGA扩展支持的修改类型与标准信号分析仪和信号发生器的基于记录的采集和生成模式相一致。

图17. 仪器驱动FPGA扩展架构包含VST仪器设计库,并且增加了一个抽取层以保护组件。用户IP不在此代码中,由主机进行控制,并且不受预编译封闭源NI-RFSA和NI-RFSG的影响

5. 大型FPGA开发考虑事项

The Virtex-6 LX195T FPGA on the NI PXIe-5644R and the NI PXIe-5645R is a large FPGA, though the full suite of instrument design libraries consumes a considerable fraction of the available resources. As such, compilation times can take 5 hours or more when using the NI LabVIEW FPGA Compile Cloud Service, depending on the complexity and resource utilization of the FPGA design. Furthermore, FPGA compilation is a non-deterministic process, and as a design consumes more FPGA resources, the repeatable compilation success rate drops below 100%. For such designs, initiating multiple compiles in parallel can help to ensure a successful compilation in approximately the same time as a single compilation. Table 3. provides some estimates for the different FPGA designs discussed in this paper.

| FPGA设计 | 近似编译时间 | 近似编译成功率 | LUT占用率 | 触发器占用率 | DSP片占用率 | 块RAM占用率 |

| VST Streaming项目范例 | 4 小时 | 90% | 27% | 30% | 31% | 20% |

| Simple VSA/VSG项目范例 | 5 小时 | 80% | 50% | 49% | 31% | 39% |

| 仪器驱动FPGA扩展 | 6 小时 | 75% | 67% | 62% | 31% | 45% |

表3. 各种VST FPGA设计的编译时间、成功率和FPGA占用率。